电子元件是现代科技社会的基石,从智能手机到航天器,其制造过程融合了材料科学、物理学、化学和精密工程的尖端技术。本文将从基础到高级,系统解析电子元件的制造流程、关键技术及未来趋势。

一、 基础制造流程:从原材料到基础元件

电子元件的制造始于最基础的原材料,主要是高纯度硅(纯度通常高达99.9999999%,即9N级)。其核心流程可概括为以下几个关键阶段:

- 晶圆制备:将多晶硅在高温单晶炉中熔化,通过提拉法(CZ法)或区熔法(FZ法)生长出圆柱形的单晶硅锭,随后将其切割成厚度不足1毫米的薄片,即“晶圆”。

- 光刻与图形化:这是微电子制造的核心。在晶圆表面涂覆光刻胶,通过掩膜版,利用紫外光、深紫外光(DUV)或极紫外光(EUV)进行曝光,将复杂的电路图形“印刷”到硅片上。此步骤的精度决定了元件的特征尺寸。

- 刻蚀与掺杂:

- 刻蚀:使用化学或物理方法,将未被光刻胶保护部分的材料去除,形成三维结构。分为湿法刻蚀(使用化学溶液)和干法刻蚀(如等离子体刻蚀)。

- 掺杂:通过离子注入或热扩散工艺,将硼、磷等杂质原子引入硅的特定区域,改变其电导率,从而形成晶体管所需的P-N结。

- 薄膜沉积:通过化学气相沉积(CVD)、物理气相沉积(PVD)或原子层沉积(ALD)等技术,在晶圆表面生长或沉积绝缘层(如二氧化硅)、导电层(多晶硅、金属)等薄膜。

- 互连与封装:经过上百道工序后,单个晶圆上可形成数十亿个晶体管。通过金属化工艺(通常使用铜互连)将这些晶体管连接成电路。晶圆被切割成单个芯片(Die),经过引线键合或倒装焊封装到外壳中,成为可用的电子元件。

二、 关键进阶技术与挑战

随着摩尔定律的推进,制造技术不断向物理极限迈进,催生了众多高级技术:

- 极紫外光刻(EUV):当特征尺寸缩小至7纳米及以下时,传统光刻波长已无法满足需求。EUV使用波长仅13.5纳米的极紫外光,配合复杂的反射式光学系统,实现了更精细的图形化,但设备极其昂贵且工艺复杂。

- 三维结构集成:为了在单位面积内集成更多晶体管,技术从平面走向立体。例如:

- FinFET晶体管:将导电沟道从平面改为鱼鳍状的立体结构,增强了栅极控制能力,大幅降低了功耗。

- 3D NAND闪存:将存储单元垂直堆叠,如同摩天大楼,在更小面积上实现了TB级的存储容量。

- 芯粒(Chiplet)与先进封装:将不同工艺、功能的芯片(如CPU、GPU、I/O芯粒)通过硅中介层、TSV(硅通孔)等技术高密度封装在一起,形成异构集成系统,提升了性能并降低了成本。

- 新材料应用:

- 高-K金属栅(HKMG):用铪基等高介电常数材料替代二氧化硅作为栅极绝缘层,有效抑制漏电流。

- 新沟道材料:研究锗硅(SiGe)、III-V族化合物(如砷化镓)乃至二维材料(如石墨烯)作为未来晶体管的沟道,以追求更高的载流子迁移率。

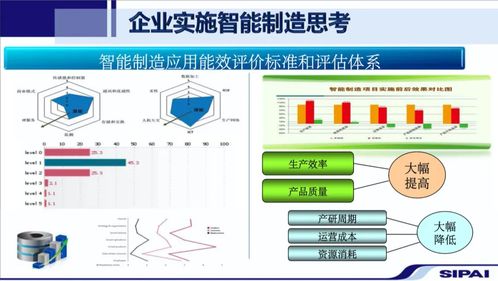

- 制造智能化与良率控制:利用人工智能和机器学习对海量制造数据进行分析,实现工艺窗口优化、缺陷实时检测和预测性维护,是提升量产良率和降低成本的关键。

三、 技术咨询与未来展望

对于企业或研发机构,在电子元件制造领域寻求技术发展或解决难题时,可关注以下咨询方向:

- 技术路线选择:针对特定产品(如高性能计算、物联网传感器、功率器件),应如何选择最合适的工艺节点(如28nm、7nm)和集成方案(SoC vs Chiplet)?

- 特色工艺开发:对于模拟、射频、高压、MEMS传感器等非数字芯片,如何设计并优化特殊的制造工艺模块?

- 供应链与生态:如何构建或融入从EDA工具、IP核、制造到封测的完整产业生态?在地缘政治背景下,供应链的韧性与安全如何保障?

- 前沿技术跟踪:下一代技术如CFET(互补场效应晶体管)、纳米片晶体管、碳纳米管芯片、量子芯片的制造路径如何?

- 可持续发展:如何降低制造过程中的巨大能耗、用水量和化学废弃物,实现绿色制造?

结论:电子元件的制造是一个持续演进、高度复杂的系统工程。从基础的材料提纯到前沿的原子级加工,每一代技术的突破都推动着信息社会的边界。超越摩尔定律的探索将与延续摩尔定律的创新并行,通过系统级架构、新材料和量子技术的融合,继续书写电子元件制造的新篇章。